破局"卡脖子"困境、國產 EDA 替代有望加速!2025年10月15日,在深圳舉辦的灣區半導體產業生態博覽會上,一場聚焦國產電子設計工具突破的發佈引發業界廣泛熱議。其中新凱來旗下子公司啟雲方科技現場推出兩款擁有完全自主知識產權的 EDA 軟體,直接填補了國產高端電子設計工業軟體的技術空白。這兩款軟體分別為原理圖設計軟體與 PCB 設計軟體,性能已達業界一流水準。它們不僅支持多人並行協同設計與隨時隨地線上檢視,還集成了智能輔助設計功能,實際應用中可將硬體產品開發週期縮短40%、一版設計成功率提升30%,能顯著提升開發效率與設計品質。當前國產 EDA 軟體行業的發展態勢如何?投資者又應重點關注哪些核心公司的投資機會?

### 國產 EDA 軟體替代有望加速,投資者應關注哪些核心公司的機會?

10 月 15 日·2025 灣區半導體產業生態博覽會(簡稱"灣芯展)在深圳舉行·一場聚焦國產電子設計工具突破的發佈引發業界熱議——新凱來科技集團旗下子公司啟雲方·首次面向全行業推出兩款具備完全自主知識產權的電子工程 EDA 設計軟體·精准覆蓋原理圖設計與 PCB(印製電路板)設計兩大核心領域·填補了國產高端 EDA 在該細分場景的技術空白。

作為半導體產業鏈上游的"工業軟體明珠"·EDA(電子設計自動化)工具長期以來在核心技術、性能指標上依賴國外廠商·國內企業面臨"卡脖子"風險。而啟雲方此次發佈的軟體·通過自主研發突破多項關鍵技術·在電子電路設計的核心評價指標上已躋身業界一流水準:相較於當前行業公認的標杆產品·其綜合性能提升30%·可高效應對複雜電路設計中的信號完整性、電源完整性等技術難題。從產業應用價值來看·這款軟體還針對性解決了傳統設計模式的痛點:支持多人並行協同設計·打破單機設計的時空限制;搭載隨時隨地線上檢視功能·可實現設計方案即時共用與回饋·大幅降低團隊溝通成本。更關鍵的是其技術優勢直接轉化為產業效率提升——能將硬體開發週期縮短40%·助力企業快速回應市場需求;內置的智能輔助設計模組·還將電路設計"一版成功率"提升30%·顯著減少反復修改帶來的時間與資源損耗。此次啟雲方在灣芯展的首發·不僅為國內電子製造、半導體企業提供了"自主可控+高性能"的EDA替代方案,更成為灣區半導體產業生態自主化建設的重要里程碑。

圖一: 新凱來科技集團電子製造產品參數情況

| 参数名称    | 说明     | 参数名称     | 说明         |

|---------|--------|----------|------------|

| Tdon    | 导通延迟时间 | Err      | 反向恢复能量     |

| Tr      | 电流上升时间 | DIDT_off | 关断正向电流下降速率 |

| Tdoff   | 关断延迟时间 | DVDT_off | 关断正向电压下降速率 |

| tf      | 电流下降时间 | DIDT_on  | 导通正向电流上升速率 |

| Eon     | 导通损耗   | DVDT_on  | 导通正向电压上升速率 |

| Eoff    | 关断损耗   | Qg       | 栅极电荷       |

| Vcepeak | 关断峰值电压 | Kelvin   | 开尔文检测      |

| Icepeak | 导通峰值电流 | Vge(th)  | 导通阈值电压     |

| Isc     | 短路电流   | Iges     | GE漏电流      |

| Irr     | 反向恢复电流 | Ices     | CE漏电流      |

| Trr     | 反向恢复时间 |          |            |

資料來源:公司官網

#### ▶國產 EDA 行業目前進程如何,潛力股有哪些?

### \*半導體產業的"上游命脈",貫穿晶片全流程的核心工具

在半導體產業從設計到製造的千億級鏈條中·EDA(電子設計自動化)軟體絕非普通輔助工具·而是決定晶片能否落地、性能能否達標、成本能否可控的"上游命脈"——它像一套精密的"數字流水線",將晶片從抽象的功能需求·完整轉化為可被晶圓廠量產的物理版圖·全程覆蓋 10 餘個核心環節·缺一不可。其具體作用貫穿晶片設計全週期:首先是需求落地階段·從電路功能構思出發·EDA 工具可完成邏輯設計與演算法建模·將"要做什麼晶片"轉化為可運算的數字邏輯電路,避免設計方向偏離實際需求;其次是風險規避階段,通過仿真驗證工具(如時序仿真、信號完整性分析)·提前排查電路中的邏輯錯誤、電壓干擾等問題·要知道·7nm以下先進制程的一次流片成本超千萬美元·EDA的仿真精度直接決定流片成功率;最後是製造銜接階段·最終通過物理設計工具·將邏輯電路轉化為符合晶圓廠工藝規則(如線寬、間距)的物理版圖·同時完成佈局佈線、功耗優化·確保設計能適配實際生產設備,實現"設計-製造"的無縫對接。

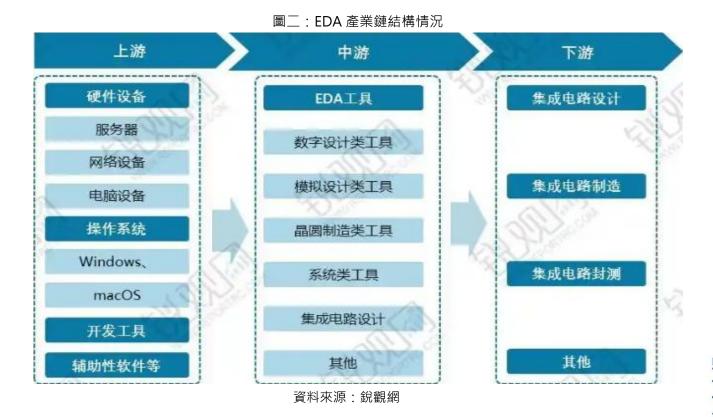

從產業鏈角度來說·EDA產業鏈上游主要包括EDA工具研發與運行的"硬體+軟體"基礎保障·涵蓋三類核心資源:一是硬體設備·包括高性能計算伺服器、圖形工作站;二是操作系統·以Linux工業級系統為主(滿足工具穩定性與相容性需求)·搭配Windows Server等輔助系統;三是底層開發與輔助軟體·包含編譯器(將代碼轉化為機器語言)、調試器(排查設計邏輯漏洞)·以及數據管理系統(存儲海量設計與仿真數據);產業鏈中游為EDA工具·即圍繞積體電路不同研發階段的需求形成

差異化解決方案:模擬設計類工具聚焦射頻晶片、電源管理晶片等領域,可完成電路拓撲設計、雜訊仿真等精細化操作;數字設計類工具針對 CPU、GPU 等複雜邏輯晶片,提供時序分析、佈局佈線、邏輯綜合等全流程支持;晶圓製造類工具則深度適配光刻、蝕刻等製造工藝,通過良率預測模型、工藝偏差分析,幫助晶圓廠降低生產損耗 ;下游環節是 EDA 工具技術價值轉化為商業價值的核心場景,直接對接積體電路產業的三類核心主體:在積體電路設計端,華為海思、中穎電子等企業借助 EDA 工具完成晶片功能設計與原型驗證;在製造端,中芯國際、長江存儲等晶圓廠通過 EDA 工具優化工藝參數、提升晶片良率;在封測端,長電科技、通富微電等企業利用 EDA 工具完成封裝方案設計與性能測試。

\*全球市場:三巨頭壟斷的"固化格局",技術與生態壁壘高築

全球市場 EDA 行業規模逐年穩健增長.據 ESD Alliance 數據.2020-2024 年全球 EDA 市場從 115 億美元增至 157 億美元.CAGR 逹 6.4%;Meticulous Research 預測 2030 年將突破 174.7 億美元.CAGR 升至 10.7%。

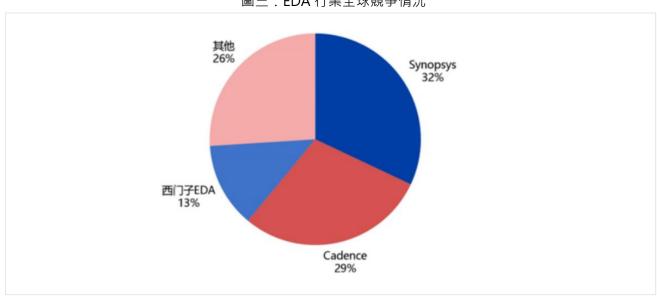

在競爭格局方面·長期以來·全球EDA市場呈現出"寡頭壟斷"的集中態勢·其中Synopsys Cadence、Siemens EDA 這三大歐美企業憑藉數十年的技術積累與生態構建·牢牢掌控著全球市場的話語權·形成難以突破的"技術護城河"。從市場份額看·三大巨頭合計佔據全球70%-80%的市場份額·其中Synopsys 以邏輯綜合、時序分析工具為核心優勢·在先進制程(3nm/2nm)設計領域市占率超30%·

深度綁定臺積電、三星等頭部晶圓廠; Cadence 聚焦定制化晶片設計(如射頻晶片、功率器件),其 EDA 設計工具全球市占率達 29%,是蘋果、高通等企業的核心供應商; Siemens EDA 在物理驗證、 測試向量生成領域優勢顯著,汽車半導體設計工具市占率居首,與博世、英飛淩等車企供應鏈深度綁 定。

圖三:EDA 行業全球競爭情況

資料來源: ESD Alliance

這種壟斷不僅體現在份額上,更體現在"技術+牛熊"的雙重壁壘:在技術壁壘上,三巨頭每年會將營 收的 15%-20%持續投入研發,這些資金並非分散使用,而是精准聚焦於 EDA 工具的核心演算法、先 進制程適配能力、多物理場仿真精度等關鍵領域,同時通過密集的專利佈局形成技術護城河。這種高 強度、高聚焦的投入,直接轉化為顯著的技術代際優勢:其工具的功能完整性、運行效率與穩定性, 始終領先國內企業 3-5 代。在先進晶片設計中,三巨頭早已實現 7nm 及以下制程的成熟商用支持,而 國產工具仍需攻克多模組協同仿真、良率優化等核心難點,短期內難以縮小差距;

在生態壁壘上·比技術差距更難突破的是生態層面的綁定。三巨頭的 EDA 工具已與全球主流晶圓廠(如 臺積電、三星)的工藝庫、頭部晶片 IP 廠商(如 ARM)的知識產權模組,形成了數十年積累的深度 適配關係。工藝庫是晶片設計與製造銜接的"翻譯器",包含晶片製造所需的材料參數、電路性能數 據;晶片 IP 則是設計中可直接複用的核心模組(如 CPU 內核、介面電路),二者與 EDA 工具的適配 精度,直接決定晶片設計的效率、成本與成品良率。國內企業若要從三巨頭工具切換至國產工具,不 僅需要重新搭建適配框架,還需完成海量的相容性測試、性能調試與良率驗證工作——整個過程往往 需要耗費數月至數年時間,同時伴隨數千萬甚至上億元的資金投入,且存在設計失敗的風險。這種極 高的時間成本與資金成本,讓多數企業即便有替代意願,也難以實際推進切換,形成了事實上的"生 熊鎖定"。

### \*中國市場:政策與需求雙驅的"破局加速期"

中國 EDA 市場雖起步比歐美晚 30 餘年,但近年來在"政策扶持+市場剛需"的雙重驅動下,已告別早期 的 "跟跑" 階段, 進入增速領先全球的"破局加速期", 成為全球 EDA 產業增長的核心引擎之一。 從市場規模看·據中國產業研究院發佈的《2024-2030 年中國 EDA 行業發展研究報告》 2024 年中國 EDA 市場規模已達 135.9 億元,較 2023 年同比增長 14%,增速是全球市場(約6%)的近 2 倍;預計 2025 年 市場規模將進一步突破 149.5 億元 · 2023-2025 年三年複合增長率將維持在 10%以上 · 顯著高於全球平均 水準。從行業結構來看,2024 年中商情報網的數據清晰顯示,EDA 行業的市場份額呈現出明顯的集中化特 徵。其中,系統級封裝與電腦輔助工具兩大板塊構成行業核心,前者占比 35.2%,後者占比 31.9%,二者 合計占比達 67.2%, 超行業整體的三分之二, 這一數據直觀凸顯出先進封裝技術與高效設計工具在行業中 的核心主導地位。

資料來源:中商產業研究院

在競爭格局方面·國內 EDA 市場呈現明顯分化特徵:國際三巨頭仍佔據主導地位·掌控著 80%的市場份額· 而整體國產化率約為 11.5%, 高端領域國產化率更是不足 2%; 與此同時, 國產 EDA 梯隊已初步形成, 其 中華大九天(301269.SZ)以 6%的市場份額成為核心玩家之一,概倫電子(688206.SH)、廣立微(301095.SZ) 緊隨其後,分別位列第二、第三,且從企業數量來看,2023 年國內 EDA 企業數量已超 120 家,較 2020 年增長3倍以上。

整體來看,國內 EDA 行業背後的驅動邏輯清晰可見:首先是政策的強力托底,EDA 被納入"卡脖子"技 術清單後,國家大基金二期、地方政府專項補貼持續向 EDA 企業傾斜,2024 年國內 EDA 企業平均獲得的 政策資金支持同比增長 35%·同時教育部新增 EDA 本科專業·有效緩解了人才短缺的痛點;其次是市場需 求的爆發,國內晶片設計企業數量已突破 3200 家 (較 2020 年增長 60%),中芯國際、長江存儲等晶圓

廠持續擴產,催生了對邏輯設計、良率優化等 EDA 工具的剛性需求,2024 年國內企業 EDA 採購量同比增長 18%;此外,國產化率提升態勢顯著,儘管當前國內 EDA 國產化率仍不足 15%,但在模擬電路、封裝設計等細分領域已實現突破(如華大九天(301269.SZ)的模擬電路工具市占率超 20%),2024 年國產 EDA企業營收合計增長 42%,遠超行業平均增速,展現出強勁的替代潛力。

#### \*投資者應該關注行業內哪些公司的投資機會?

中美在科技貿易領域的博弈不斷升級,除了傳統的半導體上游設備及高端算力晶片,以 EDA 為代表的設計輔助軟體,也逐漸成為制約中國科技產業快速發展的關鍵瓶頸。從全球市場格局來看,Mentor Graphics、Synopsys、Cadence 三大巨頭掌控著超過 70%的 EDA 市場份額;而國內 EDA 企業已形成獨特發展路徑——華大九天(301269.SZ)聚焦 EDA 工具全流程開發,概倫電子(688206.SH)主打全球驗證領域的 EDA 解決方案,廣立微(301095.SZ)則深耕 EDA 軟體與晶圓測試設備研發,三者合力構建起覆蓋設計、製造、測試全環節的差異化產品矩陣。當前,EDA 國產化替代進程正持續提速,相關領域的投資價值值得重點關注:

#### 華大九天(301269.SZ)

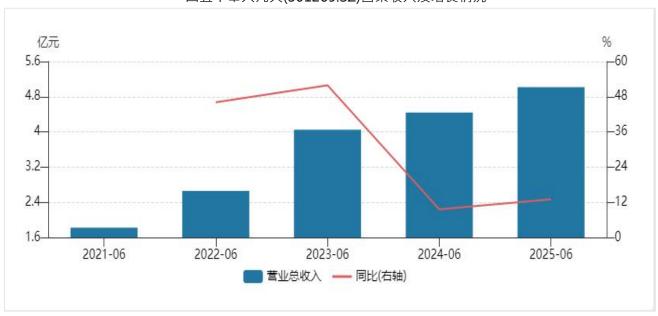

作為國內 EDA 行業的領軍企業,華大九天(301269.SZ)在國產替代浪潮中佔據關鍵地位,其核心優勢在最新財報中得到進一步印證。財報顯示,公司 2024 年實現營收 12.22 億元,同比增長 20.98%,市場份額穩居本土 EDA 企業首位;2025 年上半年營收延續增長態勢,達到 5.02 億元,同比增長 13.01%,在行業競爭加劇背景下展現出較強業務韌性。其核心優勢在於模擬電路設計全流程工具的技術突破,相關產品市占率已超 20%,且全球客戶數量近 700 家,與中芯國際等龍頭企業的深度協同更鞏固了市場地位。值得注意的是,儘管 2024 年歸母淨利潤同比下降 45.46%,但主要受高達 8.68 億元的研發投入(占營收 71.02%)及股份支付費用影響,剔除相關因素後主營業務盈利能力實則穩健,彰顯出在政策托底與技術攻堅雙重驅動下的長期價值。

從業務佈局看,華大九天(301269.SZ)構建的全流程產品矩陣在財報中呈現結構化增長亮點。2025 年上半年,核心業務 EDA 軟體銷售貢獻 4.14 億元收入,占營收比重 82.6%,仍是堅實收入基石;而技術服務業務表現尤為亮眼,實現收入 6723.94 萬元,同比大增 28.37%,成為重要增長引擎,這與國內晶片設計企業對定制化技術支持的需求爆發直接相關。更值得關注的是境外市場的突破,上半年境外收入達 5451.53 萬元,同比激增 90.39%,反映出產品海外認可度的顯著提升。研發投入的持續加碼(2025H1 研發費用占比72.84%)已轉化為具體成果,如射頻電路仿真工具 ALPSRF 通過 GPU 架構優化使仿真速度提升 10 倍以上,新推出的平板顯示電路 OPC 工具 Optimus 進一步鞏固了細分領域優勢,與國內超 3200 家晶片設計企業及晶圓廠擴產帶來的剛性需求形成正向迴圈。

從投資視角看,華大九天(301269.SZ)兼具成長確定性與稀缺性,作為 A 股罕見的 EDA 純龍頭標的,公司直接受益於國產替代提速:2024 年國內 EDA 市場規模增速達 13.3%,而公司營收增速(20.98%)遠超行業平均,且在模擬電路等領域逐步打破國際三巨頭壟斷。財務健康度方面,公司毛利率長期維持高位(2024

年93.31%)·2025年上半年經營活動淨現金流同比大增4475.6%·現金流狀況顯著改善。儘管短期受股份支付等因素影響·2025年上半年扣非淨利潤仍為-1862.1萬元·但較上年同期虧損幅度收窄63.66%·且剔除股份支付後淨利潤達1.02億元·主營業務盈利潛力凸顯。隨著高校EDA人才培養體系完善與下游需求持續釋放,公司在國產化進程中的核心地位將持續強化,長期投資價值值得重點關注。。

圖五:華大九天(301269.SZ)營業收入及增長情況

資料來源: Wind

#### 概倫電子(688206.SH)

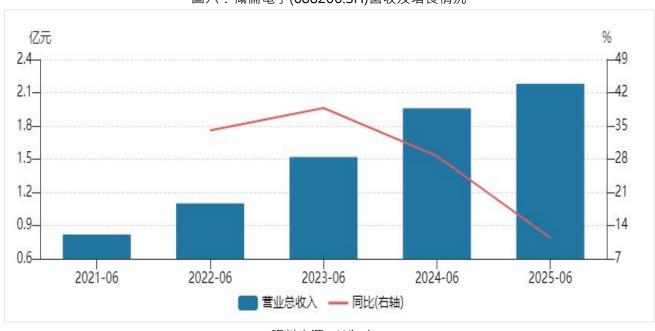

概倫電子(688206.SH)是國內 EDA 領域器件建模與仿真技術的絕對龍頭·其核心工具覆蓋 3nm 至 28nm 全制程·技術實力達到國際領先水準。公司自主研發的 NanoSpice™仿真器通過三星 3/4nm 工藝認證·可處理五千萬元件以上規模的電路仿真·性能優於其他商業 SPICE 仿真器·成為華為昇騰 910B 等高端晶片設計的必選方案。此外·其 FabLitho™光刻工藝建模工具已在國內頭部晶圓廠落地驗證·顯著提升 14nm 及以下先進制程的良率。2025 年·公司通過並購銳成芯微(全球排名第 10 的物理 IP 提供商)·形成"EDA工具 +車規級 IP"協同閉環·例如聯合開發的 5G 射頻 IP 已嵌入華為鴻蒙 OS 5.0·支撐物聯網設備微秒級通信回應。

公司財務表現持續改善・2024 年營收 4.19 億元(同比+27.42%),研發投入占比 68.9%(2.89 億元),技術攻堅力度行業領先。2025 年 Q1 實現上市後首次單季盈利(淨利潤 150 萬元),現金流顯著優化。政策層面,公司獲國家大基金二期 5 億元專項補貼,並納入上海 "積體電路重大裝備材料專項",享受研發費用加計扣除比例提至 175%等稅收優惠。2025 年 7 月,上海國資戰略入股 10 億元,重點支持 7nm 以下先進制程工具研發,預計研發週期縮短至 18 個月(行業平均 24-30 個月)。資本與政策雙輪驅動下,公司 2025 年上半年訂單同比增長超 20%,其中華為昇騰相關專案占比提升至 25%。

在全球化競爭中、概倫電子(688206.SH)通過綁定臺積電、三星等國際巨頭構建護城河。作為臺積電開放創新平臺(OIP)核心 EDA 合作夥伴、其工具鏈覆蓋 3nm 工藝開發、並接入 CoWoS 先進封裝平臺、相關收入在 2025Q1 同比增長 120%。國內市場方面、公司牽頭組建"長三角 EDA 製造協同聯盟"、與中芯國際、華虹半導體共用工藝數據、聯合開發的 14nm 車規晶片良率提升方案已實現量產應用(良率從 72%提升至 85%)。此外、公司通過並購銳成芯微(模擬 IP 全球第四)和納能微(介面 IP 國內領先)、補全汽車電子、物聯網等場景的 IP 資源、預計 2026 年 IP 授權收入占比將達 30%。長期來看、隨著國產 EDA 在模擬電路、封裝設計等領域市占率突破 40%、公司有望複製 Synopsys "工具+ IP"的價值增長路徑。

圖六:概倫電子(688206.SH)營收及增長情況

資料來源:Wind

#### 廣立微(301095.SZ)

廣立微(301095.SZ)是國內半導體良率提升領域的絕對龍頭,其技術體系覆蓋從設計到量產的全流程。公司自主研發的 EDA 工具(如 TCMagic 測試晶片設計軟體、DATAEXP 大數據分析平臺)與晶圓級電性測試設備(如 T4000 系列)形成軟硬體協同閉環,可精准定位工藝缺陷並優化良率。例如,其 DE-YMS 系統在思特威 CIS 產線應用後,推動良率從量產初期快速爬升至目標水準;WAT 測試設備的電流測試精度達 0.1pA以下,支持 3nm 先進制程開發,已進入中芯國際、華虹半導體等頭部晶圓廠供應鏈。2025 年,公司推出專為碳化矽(SiC)和氮化鎵(GaN)設計的晶圓級老化測試系統 WLBI B5260M,填補化合物半導體可靠性測試空白。截至 2024 年底,公司累計獲得 179 項專利(含 12 項美國專利),技術壁壘顯著。

公司財務表現呈現高增長+高研發投入特徵。2025 年上半年營收 2.46 億元(同比+43.17%), 歸母淨利 潤 1568 萬元(同比+518.42%), 首次實現連續季度盈利。其中、軟體開發及授權收入同比增長 50.24%, 占比提升至 37%,成為第二增長曲線。研發投入持續加碼、2025H1 研發費用 1.44 億元(占營收 58.57%), 重點突破 AI 驅動的良率分析工具(如 QuickRoot 根因定位系統)和可製造性設計(DFM)平臺。政策層

面,國家大基金二期持股 1.72%,並通過專項補貼支持其 7nm 以下工藝設備研發; 2025 年 8 月,公司以 4000 萬歐元收購全球矽光設計自動化龍頭 LUCEDA, 進一步拓展光電子集成市場。充沛的在手訂單 (4.96 億元)為未來業績提供強支撐。

在國產替代與技術迭代雙重驅動下·廣立微(301095.SZ)的 EDA 業務通過生態綁定與全球化佈局構建起競 爭護城河。國內市場中,其 EDA 工具牽頭參與"長三角 EDA-製造協同聯盟",與中芯國際、華虹半導體 共用工藝數據·聯合開發的 4nm 工藝測試方案已進入量產驗證階段·成為晶圓廠先進制程研發的核心夥伴。 國際層面·EDA 工具通過臺積電開放創新平臺(OIP)認證·接入 CoWoS 先進封裝生態·海外收入占比穩 定在 30%以上,三星 3nm 產線已導入其良率分析 EDA 模組。在新興賽道,EDA 業務已實現多領域突破: 針對第三代半導體·開發適配 SiC/GaN 的可靠性測試 EDA 工具·切入新能源汽車功率晶片市場;面向 AI 晶片·其 DFT 解決方案可應對超大規模 SoC 的測試挑戰‧適配算力晶片量產需求。長期來看‧隨著國內 EDA 國產化率向 40%目標邁進·疊加矽光晶片、先進封裝等新興領域需求爆發·廣立微(301095.SZ)的 EDA 業務將依託 "工具+設備+數據"的協同優勢,複製國際巨頭"軟體定義製造"的成長路徑,成為良率提升 領域的全球核心玩家。

圖七:廣立微(301095.SZ)公司營收增長情況

資料來源: Wind

免責聲明:本報內容所提供資料所述或與其相關的任何投資或潛在交易,均受限於閣下司法轄區適用的法律及監管規定,而 閣下須單獨就遵守該等法律及監管規定負責。本報內容僅供參考,不構成任何投資建議。本公司對所提供的財經資訊已力求 準確,但對其中全部或部分內容的準確性、完整性或有效性,不承擔任何責任或提供任何形式保證。如有錯失遺漏,本公司 恕不負責。另請注意證券與虛擬資產價格可升可跌,尤其虛擬資產的風險極高,投資者應對有關產品保持審慎及自行承擔投 資風險。